#include <FePGA.h>

Public Types | |

| typedef unsigned long | U32 |

| typedef unsigned short | U16 |

| typedef unsigned char | U8 |

Public Types inherited from Attrib Public Types inherited from Attrib | |

| enum | Attribut { UNDEFINED, PASSIVE, ACTIVE, INTERFACE, IO, IODATA, ELEMENT, HARDWARE, PROCESSUS, SOFTWARE } |

Public Member Functions | |

| FePGA () | |

| virtual | ~FePGA () |

| void | help () |

| Destructor. More... | |

| StatusCode | init () |

| void | reset () |

| void | resetUsb () |

| UsbFTMLInterface * | usb () |

| UsbMLI2cBus * | i2c () |

| UsbMLSpiBus * | spi () |

| void | update () |

| Register * | setupReg () |

| Register * | masterI2cReg () |

| Register * | addI2cReg () |

| StatusCode | testSequence () |

| StatusCode | setSpiGBTSCA (bool) |

| bool | spiGBTSCA () |

| StatusCode | setSpiAdd (unsigned long int) |

| unsigned long int | spiAdd () |

| StatusCode | setSpiSubAdd (unsigned long int) |

| unsigned long int | spiSubAdd () |

| StatusCode | spiRead (unsigned int, unsigned int, unsigned int *) |

| StatusCode | spiWrite (unsigned int, unsigned int, unsigned int *) |

| PyObject * | spiRead (unsigned int, unsigned int) |

| StatusCode | spiWrite (unsigned int, unsigned int, PyObject *) |

| unsigned int | spiRead (unsigned int) |

| StatusCode | spiWrite (unsigned int, unsigned int) |

| StatusCode | setI2cGBTSCA (bool) |

| bool | i2cGBTSCA () |

| StatusCode | setI2cBuffer (unsigned long int) |

| unsigned long int | i2cBuffer () |

| unsigned long int | i2cData () |

| StatusCode | setI2cAdd (unsigned long int) |

| unsigned long int | i2cAdd () |

| StatusCode | setI2cSubAdd (unsigned long int) |

| unsigned long int | i2cSubAdd () |

| StatusCode | i2cRead () |

| StatusCode | i2cWrite () |

| unsigned long int | i2cRead (unsigned long int) |

| StatusCode | i2cWrite (unsigned long int, unsigned long int) |

| StatusCode | transmitSpi () |

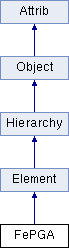

Public Member Functions inherited from Element Public Member Functions inherited from Element | |

| Element () | |

| Standard constructor. More... | |

| virtual | ~Element () |

| Destructor. More... | |

| void | recursiveInitElement () |

| void | recursiveInitCommunications () |

| StatusCode | setConnection (Hierarchy *) |

| Hierarchy * | connection () |

Public Member Functions inherited from Hierarchy Public Member Functions inherited from Hierarchy | |

| Hierarchy () | |

| Standard constructor. More... | |

| virtual | ~Hierarchy () |

| Destructor. More... | |

| void | clear () |

| void | setParent (Hierarchy *parent) |

| Hierarchy * | parent () |

| Hierarchy * | parent (std::string) |

| Hierarchy * | origin () |

| virtual void | addChild (Hierarchy *element) |

| std::vector< Hierarchy * > | children () |

| Hierarchy * | child (std::string) |

| Hierarchy * | childTyped (std::string) |

| unsigned long | numberOfChildren () |

| bool | hasChildren () |

| void | delChild (Hierarchy *) |

| void | delChild (std::string) |

| std::string | path (std::string=std::string("")) |

| std::string | pathTyped (std::string=std::string("")) |

| void | tree (std::string indent=std::string("")) |

| void | tree () |

Public Member Functions inherited from Object Public Member Functions inherited from Object | |

| Object () | |

| Standard constructor. More... | |

| virtual | ~Object () |

| Destructor. More... | |

| std::string | name () const |

| std::string | type () |

| unsigned char | id () |

| std::string | title () |

| void | msgSvc (int level, std::string msg, std::string name) |

| void | msg (std::string mymsg) |

| void | verbose (std::string mymsg) |

| void | debug (std::string mymsg) |

| void | info (std::string mymsg) |

| void | warning (std::string mymsg) |

| void | error (std::string mymsg) |

| void | fatal (std::string mymsg) |

| void | msg (std::string mymsg, std::string name) |

| void | verbose (std::string mymsg, std::string name) |

| void | debug (std::string mymsg, std::string name) |

| void | info (std::string mymsg, std::string name) |

| void | warning (std::string mymsg, std::string name) |

| void | error (std::string mymsg, std::string name) |

| void | fatal (std::string mymsg, std::string name) |

| void | setName (std::string name) |

| void | setType (std::string type) |

| void | setId (unsigned char id) |

| void | setTitle (std::string title) |

| void | setDllName (std::string dllName) |

| std::string | dllName () |

Public Member Functions inherited from Attrib Public Member Functions inherited from Attrib | |

| Attrib () | |

| Standard constructor. More... | |

| virtual | ~Attrib () |

| Destructor. More... | |

| bool | is (int attribut) |

| void | add (int attribut) |

| void | remove (int attribut) |

| std::string | attributs () |

Private Member Functions | |

| Register * | MakeRegister (std::string name, unsigned int add) |

| RAM * | MakeRAM (std::string name, unsigned int add) |

Private Attributes | |

| UsbFTMLInterface * | m_usb |

| UsbMLI2cBus * | m_usbi2c |

| UsbMLSpiBus * | m_usbspi |

| Register * | m_transmitSpiReg |

| Register * | m_ctrlSpiReg |

| Register * | m_addSpiReg |

| RAM * | m_txSpiFifo |

| RAM * | m_rxSpiFifo |

| RAM * | m_testFifo |

| Register * | m_setupReg |

| Register * | m_resetReg |

| Register * | m_testSeqReg |

| unsigned int | m_spiSubAdd |

| unsigned int | m_i2cSubAdd |

| unsigned int | m_i2cBuffer |

| Register * | m_masterI2cReg |

| Register * | m_addI2cReg |

Additional Inherited Members | |

Protected Attributes inherited from Element Protected Attributes inherited from Element | |

| Hierarchy * | m_connection |

Protected Attributes inherited from Attrib Protected Attributes inherited from Attrib | |

| std::string | m_attribString [10] |

Detailed Description

Member Typedef Documentation

◆ U16

| typedef unsigned short FePGA::U16 |

◆ U32

| typedef unsigned long FePGA::U32 |

◆ U8

Constructor & Destructor Documentation

◆ FePGA()

| FePGA::FePGA | ( | ) |

Definition at line 29 of file FePGA.cpp.

References Attrib::add(), Hierarchy::addChild(), Object::debug(), Attrib::ELEMENT, Attrib::HARDWARE, m_addSpiReg, m_ctrlSpiReg, m_resetReg, m_rxSpiFifo, m_setupReg, m_testFifo, m_transmitSpiReg, m_txSpiFifo, m_usb, MakeRAM(), MakeRegister(), Object::setId(), Object::setName(), and Object::setType().

◆ ~FePGA()

Member Function Documentation

◆ addI2cReg()

|

inline |

◆ help()

|

inlinevirtual |

Destructor.

printout help for the element

Implements Element.

Definition at line 36 of file FePGA.h.

References Object::info(), and Object::name().

◆ i2c()

|

inline |

◆ i2cAdd()

| unsigned long int FePGA::i2cAdd | ( | ) |

Definition at line 404 of file FePGA.cpp.

References IOdata::dataU8(), IOobject::io(), m_addI2cReg, and IOobject::read().

Referenced by testSequence().

◆ i2cBuffer()

| unsigned long int FePGA::i2cBuffer | ( | ) |

◆ i2cData()

| unsigned long int FePGA::i2cData | ( | ) |

Definition at line 391 of file FePGA.cpp.

References IOdata::dataU8(), IOobject::io(), and m_masterI2cReg.

Referenced by i2cRead(), and testSequence().

◆ i2cGBTSCA()

| bool FePGA::i2cGBTSCA | ( | ) |

Definition at line 371 of file FePGA.cpp.

References IOdata::dataU8(), IOobject::io(), m_setupReg, and IOobject::read().

Referenced by testSequence().

◆ i2cRead() [1/2]

| StatusCode FePGA::i2cRead | ( | ) |

Definition at line 427 of file FePGA.cpp.

References shell::data(), IOdata::dataU8(), Object::debug(), IOdata::defDataU8(), IOobject::io(), m_i2cSubAdd, m_masterI2cReg, m_setupReg, IOobject::read(), IOdata::setU8(), StatusCode::SUCCESS, and IOobject::write().

Referenced by i2cRead(), and testSequence().

◆ i2cRead() [2/2]

| unsigned long int FePGA::i2cRead | ( | unsigned long int | subadd | ) |

◆ i2cSubAdd()

| unsigned long int FePGA::i2cSubAdd | ( | ) |

◆ i2cWrite() [1/2]

| StatusCode FePGA::i2cWrite | ( | ) |

Definition at line 451 of file FePGA.cpp.

References shell::data(), IOdata::dataU8(), Object::debug(), IOdata::defDataU8(), IOobject::io(), m_i2cBuffer, m_i2cSubAdd, m_masterI2cReg, m_setupReg, IOobject::read(), IOdata::setU8(), and IOobject::write().

Referenced by i2cWrite(), and testSequence().

◆ i2cWrite() [2/2]

| StatusCode FePGA::i2cWrite | ( | unsigned long int | subadd, |

| unsigned long int | value | ||

| ) |

Definition at line 479 of file FePGA.cpp.

References i2cWrite(), setI2cBuffer(), and setI2cSubAdd().

◆ init()

|

inlinevirtual |

init the component

- Returns

- void

Implements Element.

Definition at line 42 of file FePGA.h.

References StatusCode::SUCCESS.

◆ MakeRAM()

|

private |

Definition at line 65 of file FePGA.cpp.

References Hierarchy::addChild(), IOobject::io(), m_usb, IOdata::setAddress(), Object::setName(), and RAM::setSize().

Referenced by FePGA(), and transmitSpi().

◆ MakeRegister()

|

private |

Definition at line 52 of file FePGA.cpp.

References Hierarchy::addChild(), IOdata::Byte, IOdata::defDataU8(), IOobject::io(), m_usb, IOdata::setAddress(), Object::setName(), and IOdata::setWordSize().

Referenced by FePGA(), and transmitSpi().

◆ masterI2cReg()

|

inline |

◆ reset()

|

inlinevirtual |

Resets the Element so that is is in a standard and safe situation. Different from Element::init which configure the Element. Element::reset() is more an Emergency pull. It is often/usually called by the recursiveInitElement method at the start of the program.

Implements Element.

Definition at line 54 of file FePGA.h.

References Object::info(), IOobject::io(), m_resetReg, IOdata::setU8(), and IOobject::write().

Referenced by CU_v1::reset().

◆ resetUsb()

|

inline |

Definition at line 63 of file FePGA.h.

References IOobject::dump(), Object::info(), IOobject::io(), m_resetReg, IOdata::setU8(), and IOobject::write().

◆ setI2cAdd()

| StatusCode FePGA::setI2cAdd | ( | unsigned long int | value | ) |

Definition at line 398 of file FePGA.cpp.

References IOobject::io(), m_addI2cReg, IOdata::setU8(), and IOobject::write().

Referenced by testSequence().

◆ setI2cBuffer()

| StatusCode FePGA::setI2cBuffer | ( | unsigned long int | value | ) |

Definition at line 379 of file FePGA.cpp.

References m_i2cBuffer, and StatusCode::SUCCESS.

Referenced by i2cWrite(), and testSequence().

◆ setI2cGBTSCA()

| StatusCode FePGA::setI2cGBTSCA | ( | bool | value | ) |

Definition at line 362 of file FePGA.cpp.

References shell::data(), IOdata::dataU8(), IOobject::io(), m_setupReg, IOobject::read(), IOdata::setU8(), and IOobject::write().

Referenced by testSequence().

◆ setI2cSubAdd()

| StatusCode FePGA::setI2cSubAdd | ( | unsigned long int | value | ) |

Definition at line 412 of file FePGA.cpp.

References m_i2cSubAdd, and StatusCode::SUCCESS.

Referenced by i2cRead(), i2cWrite(), and testSequence().

◆ setSpiAdd()

| StatusCode FePGA::setSpiAdd | ( | unsigned long int | value | ) |

Definition at line 77 of file FePGA.cpp.

References IOobject::io(), m_addSpiReg, IOdata::setU8(), and IOobject::write().

Referenced by BOOST_PYTHON_MODULE(), and testSequence().

◆ setSpiGBTSCA()

| StatusCode FePGA::setSpiGBTSCA | ( | bool | value | ) |

Definition at line 211 of file FePGA.cpp.

References shell::data(), IOdata::dataU8(), IOobject::io(), m_setupReg, IOobject::read(), IOdata::setU8(), and IOobject::write().

Referenced by BOOST_PYTHON_MODULE(), and testSequence().

◆ setSpiSubAdd()

| StatusCode FePGA::setSpiSubAdd | ( | unsigned long int | value | ) |

◆ setupReg()

|

inline |

◆ spi()

|

inline |

◆ spiAdd()

| unsigned long int FePGA::spiAdd | ( | ) |

Referenced by testSequence().

◆ spiGBTSCA()

| bool FePGA::spiGBTSCA | ( | ) |

Definition at line 220 of file FePGA.cpp.

References IOdata::dataU8(), IOobject::io(), m_setupReg, and IOobject::read().

Referenced by testSequence().

◆ spiRead() [1/3]

| StatusCode FePGA::spiRead | ( | unsigned int | subadd, |

| unsigned int | nwords, | ||

| unsigned int * | values | ||

| ) |

Definition at line 102 of file FePGA.cpp.

References IOdata::dataU8(), IOobject::io(), m_ctrlSpiReg, m_rxSpiFifo, m_transmitSpiReg, m_txSpiFifo, IOobject::read(), RAM::setSize(), IOdata::setU8(), and IOobject::write().

Referenced by BOOST_PYTHON_MODULE(), CU_v1::readFifo(), and testSequence().

◆ spiRead() [2/3]

| PyObject * FePGA::spiRead | ( | unsigned int | subadd, |

| unsigned int | nwords | ||

| ) |

Definition at line 144 of file FePGA.cpp.

References IOdata::dataU8(), IOobject::io(), m_ctrlSpiReg, m_rxSpiFifo, m_transmitSpiReg, m_txSpiFifo, IOobject::read(), RAM::setSize(), IOdata::setU8(), and IOobject::write().

◆ spiRead() [3/3]

| unsigned int FePGA::spiRead | ( | unsigned int | subadd | ) |

Definition at line 187 of file FePGA.cpp.

References IOdata::dataU8(), IOobject::io(), m_ctrlSpiReg, m_rxSpiFifo, m_transmitSpiReg, m_txSpiFifo, IOobject::read(), RAM::setSize(), IOdata::setU8(), and IOobject::write().

◆ spiSubAdd()

| unsigned long int FePGA::spiSubAdd | ( | ) |

◆ spiWrite() [1/3]

| StatusCode FePGA::spiWrite | ( | unsigned int | subadd, |

| unsigned int | nwords, | ||

| unsigned int * | values | ||

| ) |

Definition at line 84 of file FePGA.cpp.

References IOobject::io(), m_ctrlSpiReg, m_transmitSpiReg, m_txSpiFifo, RAM::setSize(), IOdata::setU8(), and IOobject::write().

Referenced by BOOST_PYTHON_MODULE(), and testSequence().

◆ spiWrite() [2/3]

| StatusCode FePGA::spiWrite | ( | unsigned int | subadd, |

| unsigned int | nwords, | ||

| PyObject * | value | ||

| ) |

Definition at line 124 of file FePGA.cpp.

References IOobject::io(), m_ctrlSpiReg, m_transmitSpiReg, m_txSpiFifo, RAM::setSize(), IOdata::setU8(), and IOobject::write().

◆ spiWrite() [3/3]

| StatusCode FePGA::spiWrite | ( | unsigned int | subadd, |

| unsigned int | value | ||

| ) |

Definition at line 171 of file FePGA.cpp.

References IOobject::io(), m_ctrlSpiReg, m_transmitSpiReg, m_txSpiFifo, RAM::setSize(), IOdata::setU8(), and IOobject::write().

◆ testSequence()

|

inline |

Definition at line 102 of file FePGA.h.

References i2cAdd(), i2cBuffer(), i2cData(), i2cGBTSCA(), i2cRead(), i2cSubAdd(), i2cWrite(), Object::info(), m_testSeqReg, setI2cAdd(), setI2cBuffer(), setI2cGBTSCA(), setI2cSubAdd(), setSpiAdd(), setSpiGBTSCA(), setSpiSubAdd(), spiAdd(), spiGBTSCA(), spiRead(), spiSubAdd(), spiWrite(), and IOobject::write().

◆ transmitSpi()

|

inline |

Definition at line 163 of file FePGA.h.

References Attrib::add(), m_transmitSpiReg, MakeRAM(), MakeRegister(), Object::name(), and IOobject::write().

◆ update()

|

inlinevirtual |

Update the Element configuration from the actual hardware

Implements Element.

Definition at line 93 of file FePGA.h.

Referenced by AppFrame.AppFrame::deleteHardware(), ConfFrame.ConfFrame::onChange(), GraphFrame.GraphFrame::onChange(), CfgFrame.CfgFrame::onChange(), ConfFrame.ConfFrame::onEdit(), AppFrame.AppFrame::onLoad(), ConfFrame.ConfFrame::onReLoad(), GraphFrame.GraphFrame::onReLoad(), CfgFrame.CfgFrame::onReLoad(), and AppFrame.AppFrame::onReLoad().

◆ usb()

|

inline |

Member Data Documentation

◆ m_addI2cReg

|

private |

Definition at line 202 of file FePGA.h.

Referenced by addI2cReg(), i2cAdd(), and setI2cAdd().

◆ m_addSpiReg

|

private |

Definition at line 180 of file FePGA.h.

Referenced by FePGA(), and setSpiAdd().

◆ m_ctrlSpiReg

|

private |

Definition at line 179 of file FePGA.h.

Referenced by FePGA(), spiRead(), and spiWrite().

◆ m_i2cBuffer

|

private |

Definition at line 199 of file FePGA.h.

Referenced by i2cBuffer(), i2cWrite(), and setI2cBuffer().

◆ m_i2cSubAdd

|

private |

Definition at line 198 of file FePGA.h.

Referenced by i2cRead(), i2cSubAdd(), i2cWrite(), and setI2cSubAdd().

◆ m_masterI2cReg

|

private |

Definition at line 201 of file FePGA.h.

Referenced by i2cData(), i2cRead(), i2cWrite(), and masterI2cReg().

◆ m_resetReg

|

private |

Definition at line 191 of file FePGA.h.

Referenced by FePGA(), reset(), and resetUsb().

◆ m_rxSpiFifo

|

private |

◆ m_setupReg

|

private |

Definition at line 190 of file FePGA.h.

Referenced by FePGA(), i2cGBTSCA(), i2cRead(), i2cWrite(), setI2cGBTSCA(), setSpiGBTSCA(), setupReg(), and spiGBTSCA().

◆ m_spiSubAdd

|

private |

Definition at line 194 of file FePGA.h.

Referenced by setSpiSubAdd(), and spiSubAdd().

◆ m_testFifo

◆ m_testSeqReg

|

private |

Definition at line 192 of file FePGA.h.

Referenced by testSequence().

◆ m_transmitSpiReg

|

private |

Definition at line 178 of file FePGA.h.

Referenced by FePGA(), spiRead(), spiWrite(), and transmitSpi().

◆ m_txSpiFifo

|

private |

Definition at line 182 of file FePGA.h.

Referenced by FePGA(), spiRead(), and spiWrite().

◆ m_usb

|

private |

◆ m_usbi2c

|

private |

◆ m_usbspi

|

private |

The documentation for this class was generated from the following files:

1.8.13

1.8.13